发布时间:2023-04-07作者来源:金航标浏览:2584

过去,由于电子产品的工作频率比较低,信号的上升时间比较长,互连线上的信号质量不会受到影响,但是随着电子器件工作频率的不断提高,致使传输信号的质量受到严重的影响,如阻抗匹配等问题造成的反射,传输线间的影响而产生的串扰等。因此信号完整性问题几乎成为所有高速电路设计必须面临和解决的问题。

1.信号完整性基本概念

高速数字系统一般包括两方面的定义:其一是指系统的工作频率高;其二是指系统中的信号的边沿(上升沿/下降沿)变化速率快。一般认为,当系统的工作频率达到或者超过50MHz时,就称为高速数字系统。然而更为重要的是,如果信号上升沿/下降沿的变化速率很快,那么即使系统的工作频率很低也要被看作是高速数字系统。通常约定,如果信号在信号线中传播延迟大于1/6信号驱动端的上升时间,则认为此类信号是高速信号并产生传输线效应。

信号完整性(Signal Integrity,简称SI)是指信号在信号线上的质量。当电路中信号能以要求的时序、持续时间和电压幅度到达IC时,该电路就有很好的信号完整性。信号完整性差不是由某一单一因素导致的,而是板级设计中多种因素共同引起的。主要的信号完整性问题包括反射、振铃、地弹、串扰等。

1.1反射的基本原理分析

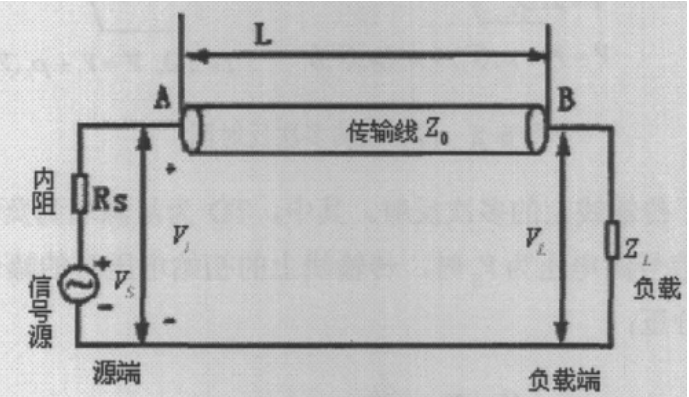

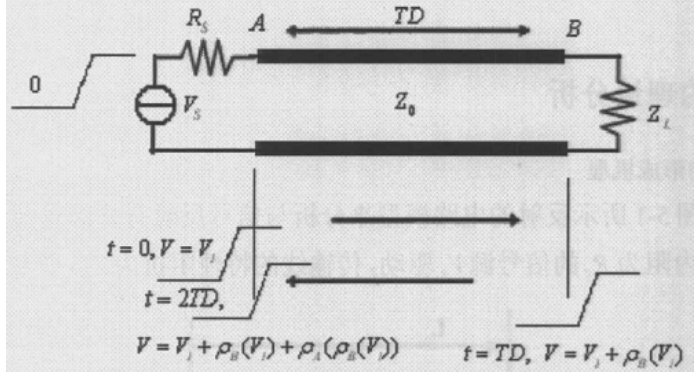

信号在传输线上进行传播时,若其路径上的瞬态阻抗在某位置处发生变化,则信号就会在该位置处产生反射,这时部分信号将会反射回去,即往信号传输相反的方向传播,这就是反射的原理。反射现象会对传输信号的质量造成非常严重的影响,[敏感词]以下图所示的反射电路模型来分析与信号反射有关的重要参数。图中,传输线L被内阻为RS的信号源VS驱动,传输线的特性阻抗为Z0,负载阻抗为ZL。

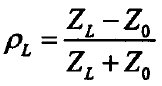

负载端阻抗与传输线阻抗不匹配会在负载端(B点)反射一部分信号回源端(A点),反射电压信号的幅值由负载反射系数ρL决定,如下式所示。

式中ρL称为负载电压反射系数,它是反射电压与入射电压之比。由上式可见,-1≤ρL≤1,且当ZL=Z0时,pL=0,这时就不会发生反射。ZL=Z0的情况称为终端匹配。只要根据传输线的特性阻抗进行终端匹配,就能消除反射。从原理上说,反射电压的幅度可以大到入射电压的幅度,极性可正可负。当ZL<z0时,ρL<0,处于过阻尼状态,反射电压极性为负;当ZL>Z0时,ρL>0,处于欠阻尼状态,反射电压极性为正。</z

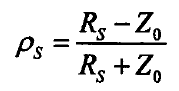

当从负载端反射回的电压在到达源端时,如果源端阻抗与传输线的特征阻抗不匹配时,就将会产生另一次离开源端的反射,形成二次反射波,此时反射电压的幅值由源反射系数ρS决定,如下式所示。

如果传输线源端和负载端都存在阻抗不匹配,信号将在源端和负载端之间来回反射,来回反射过程将需要一段比较长的时间才能达到稳定状态,这样会对时序造成重要的影响。传输线上任一点上看到的信号由入射信号和反射信号叠加而成。

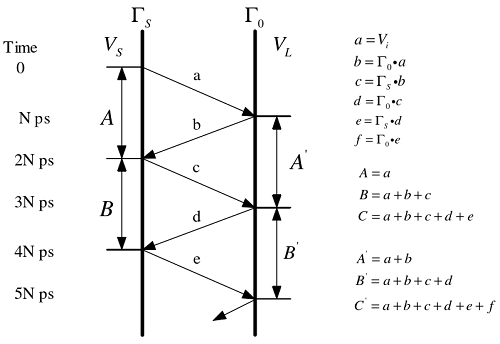

上图描述了传输线上的多次反射。其中,TD为从源端到负载端的传输线的时间延迟。当信号源电压为VS时,传输线上的初始电压Vi的幅值取决于内阻和线阻抗之间的分压:

当t=TD时,初始电压Vi到达了负载ZL,此时产生幅值为ρBVi的反射分量,它和初始电压叠加在负载处产生总电压ρBVi+Vi(其中ρB,是负载端的反射系数)。而反射分量ρBVi又传播回到源端,并在t=2TD时,产生一个由ρAρBVi决定的离开源端的反射分量(ρA是源端的反射系数)。这时源端的电压将是先前的电压Vi加上来自反射的入射瞬态电压ρBVi再加上反射波ρAρBVi。

1.2多次反射的分析

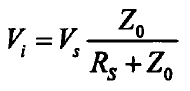

网格图(有时称为反弹图)是用于解决带线性负载传输线上多次反射的方法。以下图所示的传输线为例。

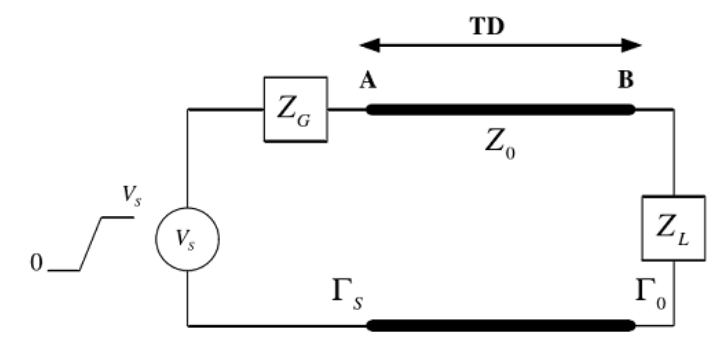

与它相应的网格图如下图所示。

左右两侧的垂直线分别代表了传输线的源端和负载端。垂直线之间的斜线代表了信号在源端和负载端之间来回反弹。图从上到下表示时间的增加。注意:时间的增量等于传输线的时间延迟。图中垂直线的顶部标识了反射系数,反射系数表示了传输线和负载之间的反射(从线看进负载)以及源端的反射系数。小写字母表示沿着传输线传播的反射信号的幅值,大写字母表示源端看到的电压,而带撇号的大写字母代表负载端看到的电压。例如,线的近端将保持A伏的电压,且持续时间为2N皮秒,其中N是传输线的时间延迟(TD)。电压A就是初始电压Vi,它将不变直到负载端的反射到达源端。电压A'就是电压a加上反射电压b。电压B就是初始电压a、负载端的反射信号b和源头端的反射信号c的总和。如此持续下去,最后负载端的电压等于VSZL/(ZG+ZL)。

1.3欠载和过载传输线的多次反射

1.3.1欠载传输线的多次反射

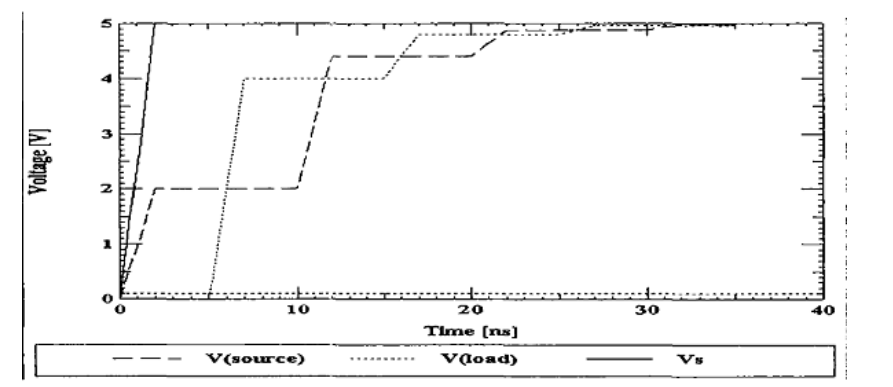

当源端阻抗ZS比传输线阻抗Z0大时,称为欠载传输线。例如,VS=5V,ZS=75Ω,传输线长28英寸(TD=5ns),Z0=50Ω,负载开路,则负载端反射系数ρload=(ZL- Z0)/(ZL+ Z0)=1,源端反射系数ρsource=(ZS- Z0)/( ZS +Z0)=0.2。当驱动器发射信号进入传输线时,传输线上呈现的初始电压为A=a=Vinitial=VSZ0/(Z0+ZS)=2V;初始信号2V将沿着传输线向负载端传播,在t=TD=5ns时到达负载,此特殊情况下,负载开路导致反射系数为1,整个信号被全部反射回源端,此时,负载端的信号为A'=2+2=4V;在 t=2TD=10ns时,2V反射信号到达源端,并产生新的反射分量c=2V*0.2=0.4V,此时,源端的电压将是B=2+2+0.4=4.4V。反射和逆反射如此持续下去,直到电压达到5V的稳态值。下图为仿真波形图。

1.3.2过载传输线的多次反射

当源端阻抗ZS比传输线阻抗Z0小时,称为过载传输线。例如,VS=5V,ZS=25Ω,传输线长28英寸(TD=5ns),Z0=50Ω,负载开路,则负载端反射系数ρload=(ZL- Z0)/(ZL+Z0)=1,源端反射系数ρsource=(ZS-Z0)/(ZS+Z0)=-0.333。当驱动器发射信号进入传输线时,传输线上呈现的初始电压为A=a=Vinitial=VSZ0/(Z0+ZS)=3.333V;初始信号3.333V将沿着传输线向负载端传播,在t=TD=5ns时到达负载,整个信号被全部反射回源端,此时,负载端的信号为A'=3.333+3.333=6.666V;在t=2TD=10ns时,3.333V反射信号到达源端,并产生新的反射分量c=3.333V*(-0.333)=-1.101V,此时,源端的电压将是B=3.333+3.333-1.101=5.565V。反射和逆反射如此持续下去,直到电压达到5V的稳态值。下图为仿真波形图。可以看到负载端Vload产生“振铃”效应。

1.4电抗性负载的反射

1.4.1容性负载的反射

当传输线终端连接一个容性负载时,源端和负载端的波形将有一个与典型传输线响应完全不同的形状。实质上,电容是时间相关负载,当信号到达电容时开始看起来是短路,而当电容完全充电之后看起来是开路。

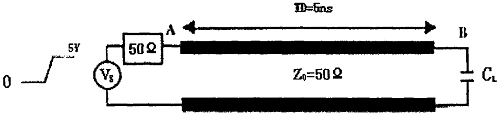

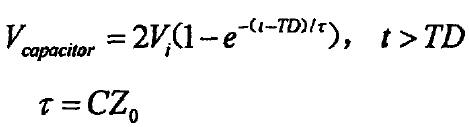

下图所示为容性负载传输线,负载电容CL为30pF,线长28英寸(TD=5ns),驱动器和传输线阻抗都是50Ω。

源端(节点A)的初始电压为Vi=VSZ0/(Z0+ZS)=2.5V;源端反射系数ρsource为0;负载端反射系数ρload在信号刚到达电容时为-1,电容完全充电之后为1。当t=TD=5ns时,幅值2.5V的初始信号已经沿着传输线传播到达容性负载,波形将被反射离开负载,反射量幅值为-2.5V,此时,信号在负载端(节点B)形成起始电压2.5V+(-2.5V)=0V;当t>TD后电容开始以决定于τ的速度充电到稳态值5V,τ是RC电路的时间常数,其中C是负载电容,R是传输线的特征阻抗Z0;当电容完全充电后类似于开路,反射系数将为1。开始于t=TD的负载电容(节点B)电压如下式:

在t=2TD=10ns时,-2.5V反射信号到达源端,此时源端(节点A)的电压将是2.5V+(-2.5V)=0V;然后随着电容充电,源端电压上升直到稳态值5V。下图为仿真波形图。

1.4.2感性负载的反射

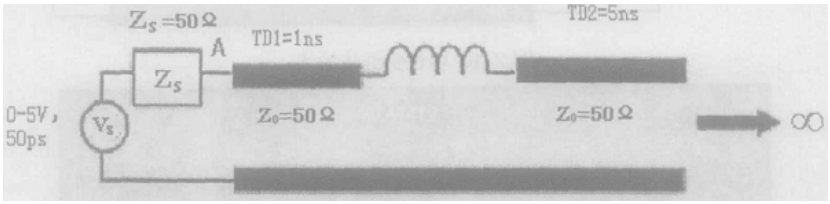

当一个串联电感出现在传输线的电气路径时,如下图所示,它也成了一个时间相关的负载。开始 t=0,电感就像开路。如果开始使用的是阶梯电压,则几乎没有电流流过电感,这使得反射系数为1。电感值的大小决定反射系数保持为1的时间,如果电感足够大,信号的幅值将加倍。最后,电感将以决定于LR电路时间常数τ(其值为L/Z0)的速度释放它的能量。

下图为仿真波形图。串联电感分别取20nH、50nH和100nH时,通过仿真可以得到在节点A看到反射的幅值和衰减时间随电感值增加而增加。

1.5抑制反射的措施

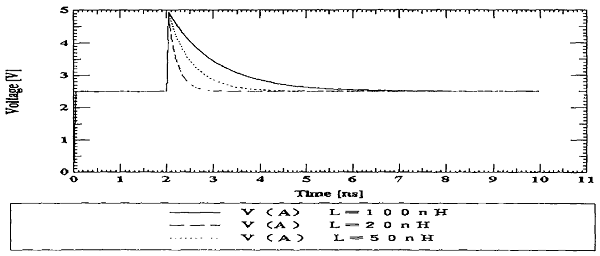

反射会在电路中造成很多问题,例如反射就是造成上冲、下冲和振荡的直接原因。如下图所示是反射信号与原信号叠加形成的上冲和下冲。因此,在高速电路设计中,如何有效地抑制反射就显得非常重要。

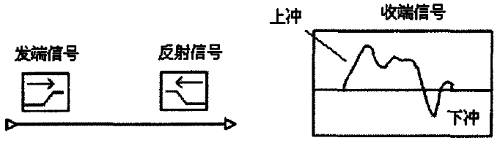

1.5.1布线拓扑法

走线的拓扑结构是指一根网线的布线顺序及布线结构。通常情形下,PCB走线可以选用下图所示的几种拓扑结构。

(1)点到点

点到点的拓扑结构,比较简单,只要在驱动端或接收端进行适当的阻抗匹配(通常情况下使用其中的一种就够了,有的电路会出现要求同时使用两种匹配的情况),便可以得到较好的信号完整性。

(2)菊花链

当网络的整个走线长度延迟小于信号的上升或下降时间时,可采用菊花链拓扑结构,布线从驱动端开始,依次到达各接收端,实际设计,我们应使菊花链布线中分支长度尽可能短。菊花链走线的优点在于:占用的布线空间较小并可用单一电阻匹配终结;在控制走线的高次谐波干扰方面,效果较好。这种走线方式缺点是:布通率低,不容易100%布通;不同的信号接收端信号的接收是不同步的。

(3)星形

一个信号驱动器驱动多个信号接收器,并要求这多个信号接收器同时接收到信号时,一般要使用星形拓扑结构,要求每个分支的接收端负载和走线长度L1尽量保持一致,每条分支上一般都需要终端电阻,终端电阻的阻值应和连线的特征阻抗相匹配。这样即使在非常快的变化沿情况下仍可以得到很好的性能。

星形拓扑结构可以有效的避免时钟信号的不同步问题,但在密度很高的PCB板上手工完成布线十分困难,可采用自动布线器完成星型布线。

(4)远端分支

远端分支跟星形类似,只不过分支是靠近接收端。在这种拓扑结构中,也要限制远端分支的长度L2,使分支上的传输延时小于信号的上升或下降时间。

(5)周期性负载

周期性负载的拓扑要求每段分支的长度L2足够小,使分支上的传输延时小于信号的上升或下降时间。这种主干传输线和所有的分

支段组合起来的结构可以看作为一段新的传输线,其特征阻抗要比原来主干传输线的特征阻抗小,传输速率也比原来的低,因此在进行阻抗匹配时要注意。

在实际的PCB设计过程中,对于关键信号,应通过信号完整性分析来决定采用哪一种拓扑结构。

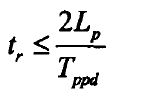

除此以外,为了将电压的过冲/下冲限制在合理的范围内(不超出稳态值的10%~15%),PCB设计布线时一般遵循以下原则:信号的上升时间要小于信号在传输线上来回引起的传输时延。即:

式中:

tr为信号的上升沿时间;

Lp为走线或传输线的长度(即信号的传播距离);

Tppd为传输线单位长度引起的时延。

1.5.2端接

根据传输线理论,传输线的长度满足

时,就应对传输线进行端接。上式中,L为传输线线长,tr为源端信号的上升时间,tpdL为传输线上每单位长度的带载传输延迟。即当tr<2LtpdL时,从传输线的接收端反射回的反射波会在源端的电平转移之前达到源端,从而叠加到源端信号上形成振铃等信号完整性问题。因此,这时就需要使用端接以消除或减少反射。

通常,传输线的端接技术有两种策略:

(1)使负载阻抗与传输线阻抗匹配;

(2)使源阻抗与传输线阻抗匹配,即串行端接。

负载端的反射系数和源端的反射系数为零,反射都会消除。策略(1)是消除了负载端的反射,即负载端的反射系数为0,消除了传输线上的一次反射。策略(2)则是消除了源端的反射,即源端的反射系数为0,消除了传输线上的二次反射。从系统设计的角度,应[敏感词]策略(1),因为这种策略消除了一次反射,从而可以减小传输线上的噪声、电磁干扰;而策略(2)只是消除二次反射,因此传输线上的电压为源信号和一次反射信号的叠加,其电压和电流会比策略(1)时更大,电磁干扰也就更大。

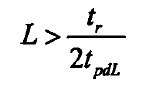

1.串联端接

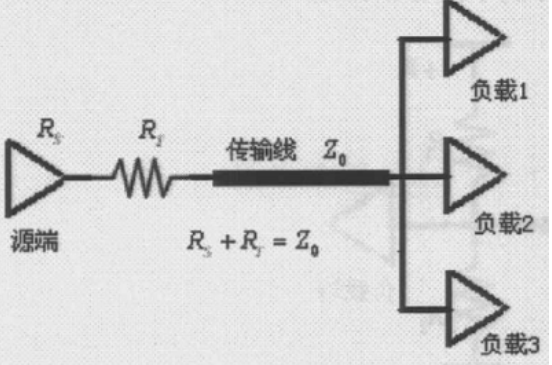

串联端接的形式如下图所示。串联端接方式指的是靠近源端的位置串联一个电阻RT以匹配信号源端的阻抗,使源端的反射系数为零从而抑制从负载反射回的信号再次从源端反射回负载端。RT加上驱动源的输出阻抗RS应等于传输线阻抗Z0,即Z0=RT+RS。

串联端接技术具有如下优点:可提供较慢的上升时间,引起更小的剩余反射及更小的EMI;当驱动高容性负载时可提供限流作用,这种限流作用可以帮助减小地弹噪声;每条线只需要一个端接电阻,无需直流电源相连接;当在走线终端上是集总负载或单一元件时,串联终端是最佳选择。

串联端接的缺点是当信号逻辑转换时,由于串联电阻的分压作用,在走线路径中间,电压仅是源电压的一半,所以不能驱动分布式负载;由于在信号通路上加接了元件,增加了RC时间常数从而减缓了负载端信号的上升时间,因而不适合用于高频信号通路(如高速时钟等)。

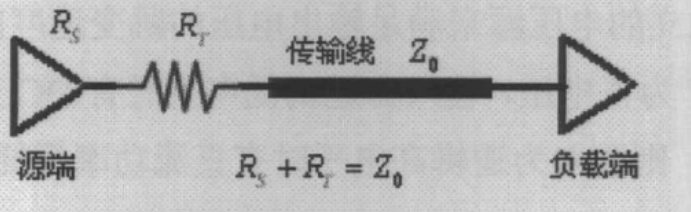

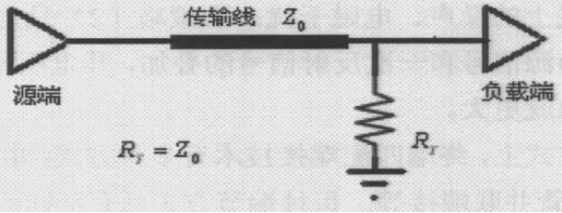

2.并联端接

并联端接技术包括下拉和上拉并联两种方式。

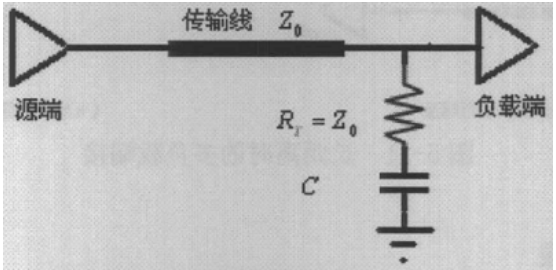

下拉并联端接(又称简单并联端接)是简单的在负载端加入一个下拉接地的电阻RT(Z0=RT)来实现终端匹配,如下图所示。采用此端接的条件是驱动端必须能够提供输出高电平时的驱动电流以保证通过端接电阻的高电平电压满足门限电压要求。

下拉并联端接的优点是:可以彻底消除反射。缺点是终端匹配电阻会带来直流功耗;会降低信号的输出电平,从而降低接收器输入端的抗噪声能力(除非驱动器可给大电流电路提供电流)。

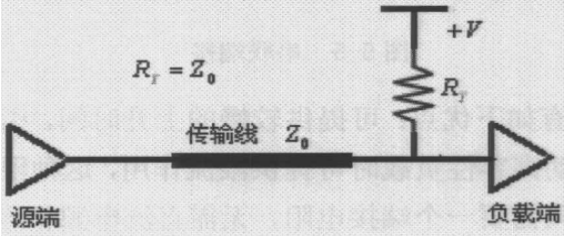

上拉并联端接又称主动并行端接,如下图所示。在此端接策略中端接电阻RT(Z0=RT)将负载端信号拉至偏移电压V。偏移电压V的选择依据是使输出驱动源能够对高低电平信号有汲取电流能力。这种端接方式的缺点是需要一个具有吸、灌电流能力的独立的电压源来满足输出电压的跳变速度的要求。在此端接方案中,如偏移电压V为正电压,输入为逻辑低电平时有直流功率损耗,如偏移电压V为负电压,则输入为逻辑高电平时有直流功率损耗。

3.戴维南端接

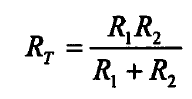

戴维南端接方式如下图所示。它采用上拉电阻R1和下拉电阻R2构成端接电阻,通过R1和R2吸收反射。R1和R2阻值的取值满足如下条件:R1的最大值由可接收的信号的最大上升时间决定,R1的最小值由驱动源的吸电流数值决定。R2的选择应满足当传输线断开时电路逻辑高电平的要求。R1和R2的戴维南等效阻抗可表示为:

要求RT等于传输线特征阻抗Z0以达到最佳匹配。

戴维南端接方式能降低对源端器件驱动能力的要求,但由于在偏移电压V和地之间连接的电阻R1和R2而一直在从系统电源吸收电流,因此直流功耗较大。戴维南端接在具有多个接收器及驱动器的工作网络的总线上将会出现延迟增加的现象,这是由于连接到网络上的所有器件提供了附加集总电容。

4.RC网络端接

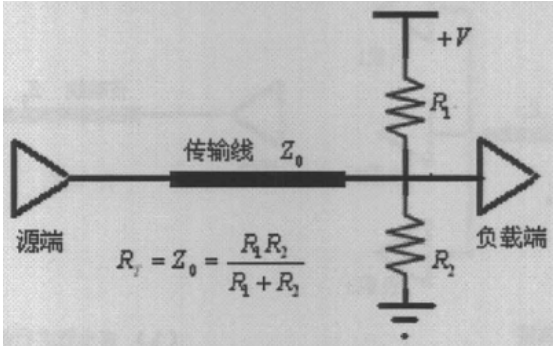

如下图所示,RC网络端接(也称为交流端接)使用串联RC网络作为端接阻抗。端接电阻R要等于传输线阻抗Z0,电容C通常使用0.1uF的多层陶瓷电容,RC网络的时间常数应大于传播延时的两倍,即RC>2TD,这样,反射将很小或被消除。

交流端接的好处在于电容阻隔了直流通路而不会产生额外的直流功耗,同时允许高频能量通过而起到了低通滤波器的作用;缺点是 RC网络的时间常数会降低信号的速率。

5.多负载端接

在实际电路中常常会遇到单一驱动源驱动多个负载的情况,这时需要根据负载情况及电路的布线拓扑结构来确定端接方式和使用端接的数量。一般情况下可以考虑以下两种方案。

如果多个负载之间的距离较近,可通过一条传输线与驱动端连接,负载都位于这条传输线的终端,这时只需要一个端接电路。如采用串行端接,则在传输线源端加入一串联电阻即可,如下图所示。

如采用并联端接(以下拉并联端接为例),则端接位置应选在离源端距离最远的负载处,同时,线网的拓扑结构应优先采用菊花链的连接方式,如下图所示。

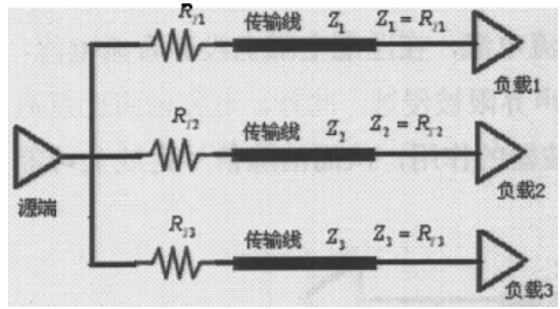

如果多个负载之间的距离较远,需要通过多条传输线与驱动端连接,这时每个负载都需要一个端接电路。如采用串行端接,则在传输线源端每条传输线上均加入一串行电阻,如下图所示。

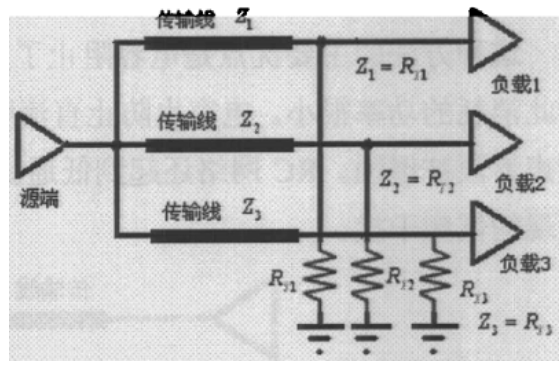

如采用并联端接(以简单并联端接为例),则应在每一负载处都进行端接,如下图所示。

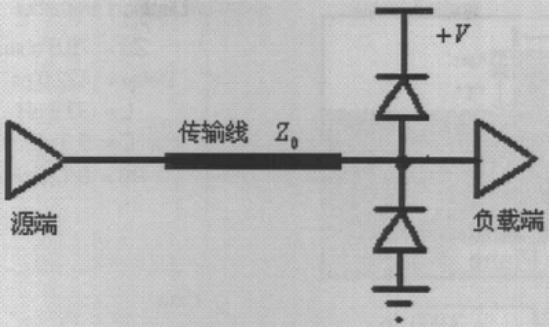

6.二极管并行端接

典型的二极管端接如下图所示。使用二极管进行终端匹配不能消除反射而只能限制反射的幅度。二极管的低正向电压降Vf将输入信号钳位到GROUND-Vf和VCC+Vf之间。这样就显著减小了信号的过冲和下冲的幅度。

使用二极管端接的好处是通过二极管钳位减小过冲与下冲,不需要进行传输线的阻抗匹配,但是由于二极管的开关速度会限制响应时间,因此不适用于高速电路。

免责声明:本文采摘自网络 e小白,本文仅代表作者个人观点,不代表金航标及行业观点,只为转载与分享,支持保护知识产权,转载请注明原出处及作者,如有侵权请联系我们删除。